## rFAS - FPGA Accelerator Sandboxing

#### FPGAs have a huge surface of attack!

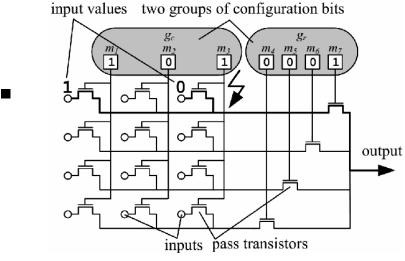

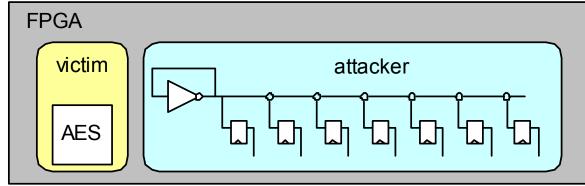

Remote DPA attacks

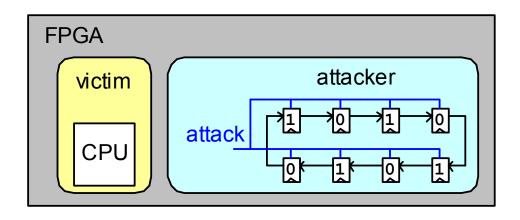

Destroy or age FPGA hardware through corrupted bitstream (we have shown that!)

Power hammering attacks

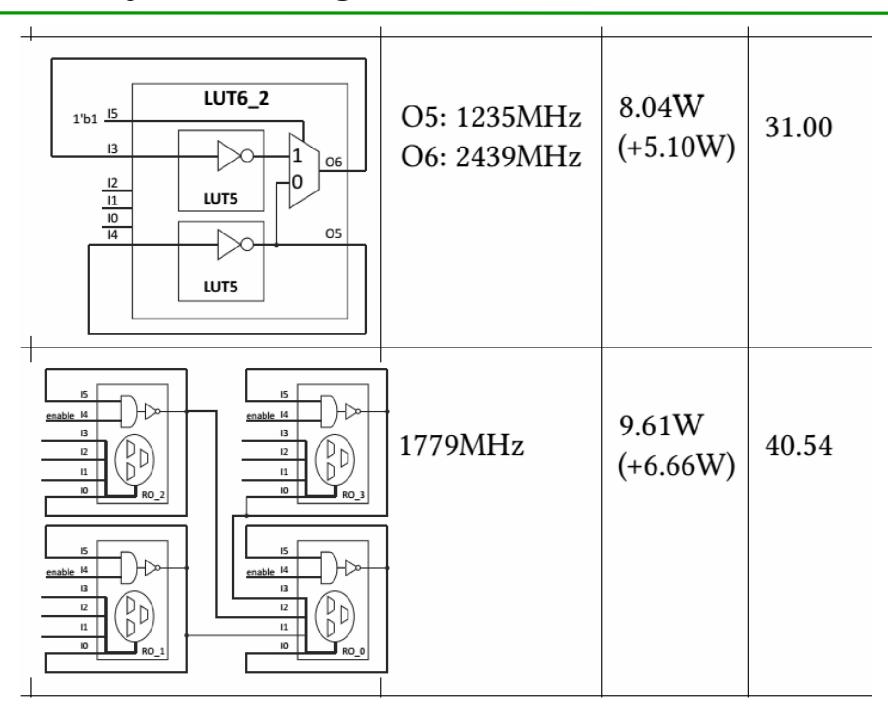

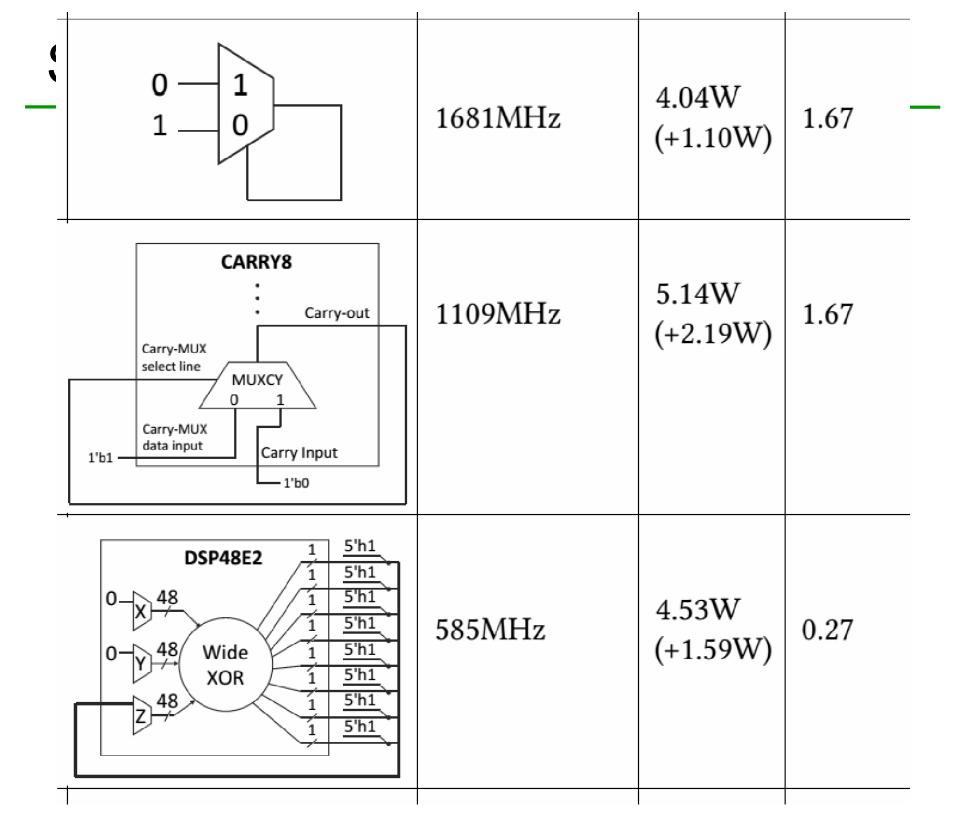

| Schematics                               | Measured Frequency | Power             | WPP   |

|------------------------------------------|--------------------|-------------------|-------|

| Ø                                        | Ø                  | 2.94W             | Ø     |

| 15<br>14<br>13<br>12<br>11<br>10<br>LUT6 | 5882MHz            | 7.32W<br>(+4.38W) | 26.63 |

| 15<br>14<br>13<br>12<br>11<br>10<br>LUT6 | 3937 MHz           | 6.84W<br>(+3.90W) | 23.69 |

| D LDCE<br>D GE<br>CLR G         | 1706MHz | 5.14W<br>(+2.19W) | 13.35 |

|---------------------------------|---------|-------------------|-------|

| PRE<br>0 D Q<br>C FDPE          | 555MHz  | 5.26W<br>(+2.32W) | 7.05  |

| FDCE external trigger  CLK  CLK | 481MHz  | 8.05W<br>(+5.10W) | 10.35 |

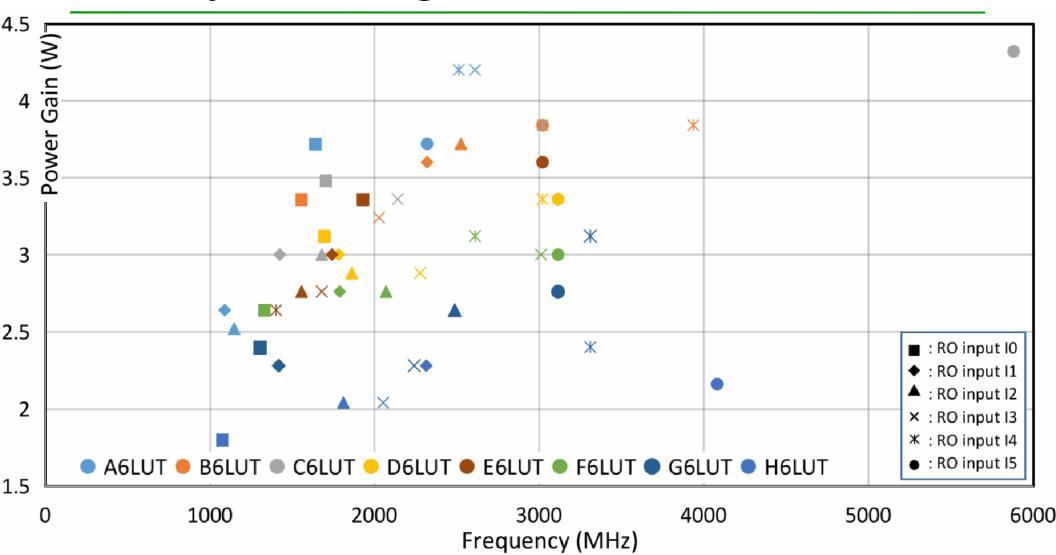

#### Experiment: 2K LUTs on a Ultra96 Board (Xilinx Zynq UltraScale+)

- The fastest oscillators do not necessary burn most power

- Fast oscillators are better for power analysis attacks

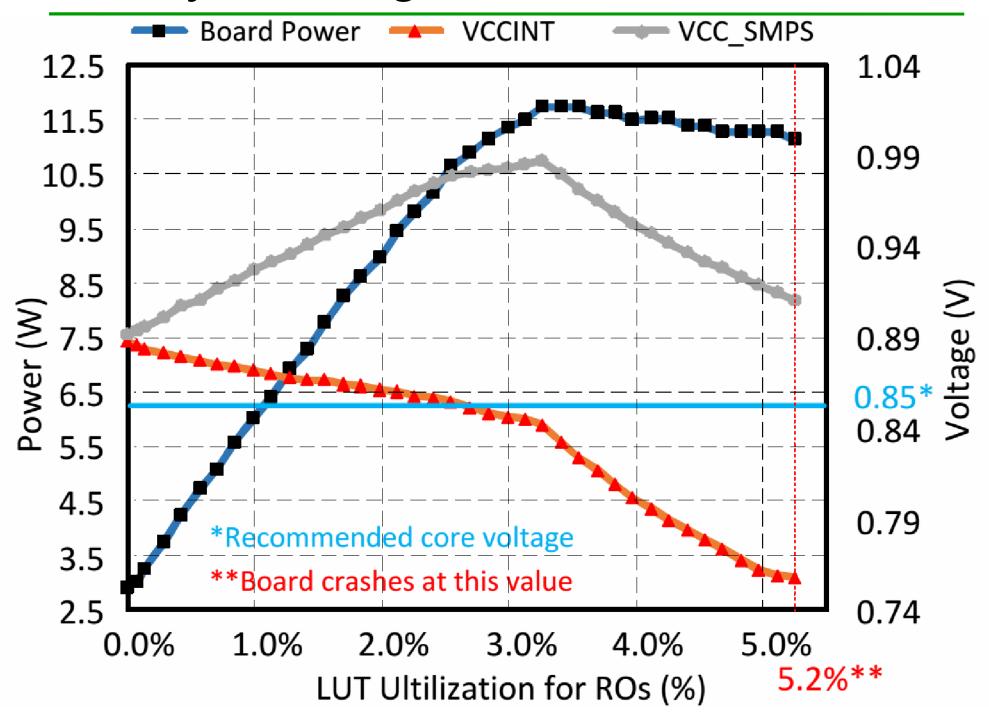

We carried out first experiments on an Alveo U200\*

datacenter FPGA → 10% LUTs draw 350W !!!

(\* same specification as used in Amazon F1)

- x KW Power-hammering potential!

- Many of our circuits are not spotted by the vendor tools!

(Design Rule Checks (DRCs) & power analyzer tool)

- We tested power-hammering attacks on Amazon F1 instances:

- → can be deployed!

- Oscillators allow power analysis attacks

(finger printing (PUFs), temperature, attack triggers, ...

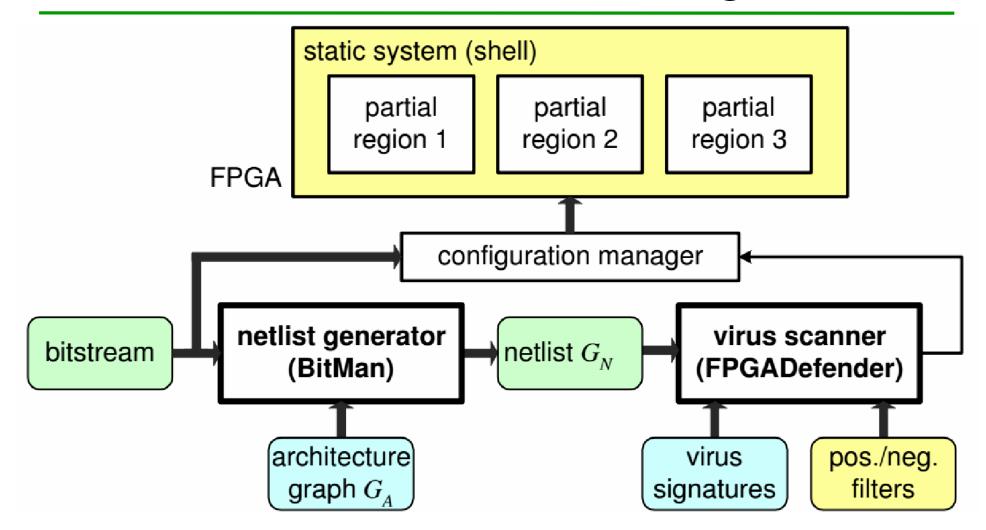

## FPGADefender Virus Scanning for FPGAs

- Detects probably any kind of self-oscillating circuits

- Scans bitstream encoding (short circuits), high fan-out nets, wire tapping, module bounding boxes (all at bitstream level)

- more to come ...

#### rFAS - FPGA Accelerator Sandboxing

#### Major outcome:

**FPGADefender**

(spinoff???)

#### People:

Tuan Minh La {tuan.la@postgrad.manchester.ac.uk}

Khoa Dang Pham {khoa.pham@manchester.ac.uk}

Kaspar Matas {kaspar.matas@manchester.ac.uk}

Nikola Grunchevski {nikola.grunchevski@manchester.ac.uk}

Dirk Koch {dirk.koch@manchester.ac.uk}