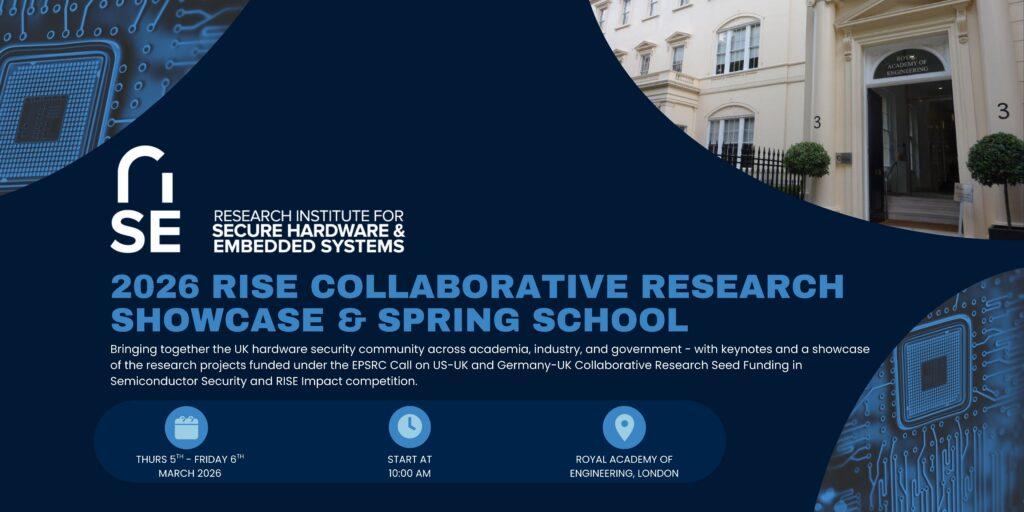

The UK Research Institute in Secure Hardware and Embedded Systems (RISE) will be holding a Research Showcase & Spring School at the Royal Academy of Engineering, London 5th – 6th March 2026.

PhD & Researcher Bursaries

Please note that a limited number bursaries are available for UK-based PhD students and post-doctoral researchers, on a first come first serve basis. Bursaries can cover accommodation for up to 2 nights and travel costs. Requests for bursaries should be sent to info@ukrise.org after registering at the above link.

Keynotes

Simon Johnson – serves as the Strategic Lead for Confidential Computing within Intel’s Office of the CTO, where he oversees technical evangelism efforts, fosters collaboration across the Confidential Computing ecosystem, and helps define and accelerate next-generation hardware capabilities. In this role, he engages closely with partners, customers and internal teams to drive secure computing innovation and adoption. Simon also serves as the Program Architect for Intel SGX, shaping its technical and strategic direction.

Prof. Dr.-Ing. Georg Sigl – is Professor of Security in Information Technology at the Technical University of Munich (TUM), where he founded and leads the Chair of Security in Electrical Engineering and Information Technology. His research spans hardware security, secure circuit and embedded system design, cryptographic implementations, and the analysis of hardware attacks, and he has published widely on these topics. After earning his PhD in Electrical Engineering at TUM in 1992, he worked in research and development at Siemens and Infineon, leading the creation of award-winning secure microcontroller platforms, and he also serves as Director at the Fraunhofer Research Institute for Applied and Integrated Security (AISEC) in Munich. Prof. Sigl’s work — bridging industry and academia — has advanced secure hardware technologies and contributed to foundational research in embedded and information security.

Conference Chair

Professor Máire O’Neill – is a world-leading expert in cybersecurity, hardware security and applied cryptography, and serves as Research Director of the Centre for Secure Information Technologies (CSIT) and Director of the EPSRC-funded Research Institute in Secure Hardware and Embedded Systems (RISE) at Queen’s University Belfast. Widely recognised as one of Europe’s foremost cryptography researchers, she invented a high-speed silicon security chip deployed in over 100 million devices and holds numerous prestigious awards and fellowships. At CSIT and RISE, she leads major international collaborations in secure communications, embedded systems security and next-generation security solutions, contributing to national and global leadership initiatives in cybersecurity and responsible technological innovation.

Agenda

| Day 1 Agenda – 5th March 2026 | |

|---|---|

| 09:00 – 10:00 | Registration – Tea / Coffee / Refreshments |

| 10:00 – 10:15 | Opening Remarks / Welcome (Professor Máire O’Neill, RISE Director) |

| 10:15 – 11:00 | Keynote: Simon Johnson, Intel Fellow & Confidential Compute Technical Director |

| Session 1: Hardware Security Vulnerabilities & Mitigations Chair: Dr Patrik Ekdahl, Ericsson |

|

| 11:00 – 11:20 | Foundations of Configurable Hardware Tracing for Monitoring Safety-Critical Systems Dr Martin Berger, University of Sussex, Professor Martin Leucker, University of Lübeck, Dr Alexander Weiss, Accemic |

| 11:20 – 11:50 | Break & Networking |

| 11:50 – 12:10 | Secure Start and Execution with Electronics Having Hardware Security Vulnerabilities Dr Amit Kumar Singh, University of Essex, Prof Prabhat Mishra, University of Florida |

| 12:10 – 12:30 | Side-Channel Analysis (SCA) and Countermeasure Implementation of Post-Quantum HQC on FPGA and ASIC Dr Anh Tuan Hoang, Queen’s University Belfast, Prof Samuel Pagliarini, Carnegie Mellon University |

| Session 2: Hardware Security Primitives & Physical Unclonable Functions (PUFs) Chair: Dr Chongyan Gu, CSIT, Queen’s University Belfast |

|

| 12:30 – 12:50 | Secure-by-Design Photonic Identification Using Inhomogeneously Broadened Quantum Dot Physical Unclonable Functions (QD-PUFs) Dr Craig Allford, Cardiff University (Authors: Prof Peter Smowton, Cardiff University; Prof John Bowers, UC Santa Barbara) |

| 12:50 – 13:10 | NeuroSecure – Building Trustworthy PUFs for Neuromorphic Chips Dr Xiaoyoa Song, Prof Merlyne De Souza, University of Sheffield, Dr Stefan Wiefels, Forschungszentrum Jülich |

| 13:10 – 14:20 | Lunch, Poster Session & Networking |

| 14:20- 14:40 | Hardware Root of Trust Reconsidered – Developing a Distributed Security Architecture to Protect Vulnerable Devices in the Semiconductor Supply Chain Dr Prosanta Gope, University of Sheffield, Dr Owen Millwood & Dr Witali Bartsch, Wiznet, Germany |

| 14:40 – 15:00 | Multi-Parameter Physically Unclonable Functions with Thin-Film Multimodal Transistors (MULTI-TRUST) Dr Radu Sporea, University of Surrey, Dr Hans Kleemann, TU Dresden |

| Session 3: RISE Impact Competition Winners Chair: Dr Louise Cushnahan, CSIT, Queen’s University Belfast |

|

| 15:00 – 15:20 | SHIELD: A New Layer of Defense with Intelligent Hardware Monitoring for Safer Embedded Systems Dr Sangeet Saha, University of Essex |

| 15:20 – 15:50 | Break & Networking |

| 15:50 – 16:10 | PaRtial Execution oF EncRypted dAta using reconfiguraBle hardware (PREFERABLE) Professor Gareth Howells, University of Essex |

| 16:10 – 16:30 | Combating fake media with edit-tolerant authentication Daniel Fentham, Professor Mark Ryan, Dr Xiao Yang, University of Birmingham |

| 16:30 | Day 1 Closing Remarks |

| 19:00 | Drinks Reception & Buffet: The Admiralty, 66 Trafalgar Square, London, WC2N 5DS |

| Day 2 Agenda – 6th March 2026 | |

|---|---|

| 09:00 – 09:30 | Registration – Tea / Coffee / Refreshments |

| 09:30 – 10:15 | Keynote: Design and Validation of RISC-V based Secure Microcontroller Chips Prof Georg Sigl, Director Institute for Applied and Integrated Security (AISEC), Fraunhofer |

| 10:15 – 10:35 | National Cyber Security Centre (NCSC) |

| 10:35 – 11:05 | Break & Networking |

| Session 4: Hardware-Rooted Security in RF, Photonic and Semiconductor Systems Chair: Professor Gareth Howell, University of Essex |

|

| 11:05 – 11:25 | Securing Device Identification Using Hardware Impairments in RF Circuits Dr Junqing Zhang, University of Liverpool, Prof Aydin Sezgin, Ruhr-Universität Bochum |

| 11:25 – 11:45 | Security of Photonic Integrated Circuits Dr Cillian McPolin, Digital Catapult, Prof. Mahdi Nikdast, Colorado State University |

| 11:45 – 12:05 | Optical Sources for Secure Timing in Critical Infrastructures Dr Samuel Shutts, Cardiff University |

| 12:05 – 12:25 | Security Assurance of Semiconductor Manufacturing (SASM) Dr Sridhar Adepu, Swansea University; Mayura Padmanabhan, SEMI |

| 12:25 – 13:40 | Lunch, Poster Session & Networking |

| Session 5: AI & Hardware Security Chair: Professor David Oswald, Durham University |

|

| 13:40 – 14:00 | Establishing a Low-Cost Platform for Advanced Security Testing of AI Hardware Dr Chongyan Gu, Queen’s University Belfast, Dr Aydin Aysu, North Carolina State University |

| 14:00 – 14:20 | Security-Enhanced AI Inference Edge Processors Dr Amro Awad, University of Oxford, Prof Hussam Amrouch, Technical University of Munich |

| 14:20 – 14:40 | AI-Sec – Secure NoC Architectures for Deep Learning Systems Dr Arnab Biswas, Queen’s University Belfast, Prof Ankur Srivastava, University of Maryland |

| 14:40 – 15:00 | RISE Updates & Future Opportunities |

| 15:00 | Closing Remarks |

This symposium is supported by the UK Department for Science, Innovation and Technology (DSIT).

Session Speakers

Dr Martin Berger – is an Associate Professor in Foundations of Computation in the School of Engineering and Informatics at the University of Sussex, where he conducts research in programming languages, formal verification, logic and the foundations of secure and reliable computation. His work spans theoretical computer science and practical advances in areas such as program synthesis, static analysis, and GPU-accelerated verification, with numerous peer-reviewed publications and contributions to international conferences and journals. Dr Berger’s scholarship includes developing techniques for analysing and reasoning about complex software systems, and he is active in the Foundations of Software Systems research group, supervising doctoral research and engaging in interdisciplinary collaborations.

Dr Amit Kumar Singh – is a Reader (Associate Professor+) in the School of Computer Science and Electronic Engineering at the University of Essex, UK, where he contributes to teaching, research and leadership in advanced computing systems. He received his B.Tech in Electronics Engineering from the Indian Institute of Technology Dhanbad and his PhD from Nanyang Technological University in Singapore, and his research focuses on the design of high-performance, energy-efficient, reliable and secure computing systems across applications including automotive, healthcare, multimedia and data centres. Dr Singh has published over 130 peer-reviewed papers, served in leadership and technical program roles for major international conferences, and sits on editorial boards for leading journals in his field, reflecting his contribution to embedded systems, multi-/many-core architectures, hardware security and sustainable computing research.

Dr Anh Tuan Hoang – is a Lecturer in the School of Electronics, Electrical Engineering and Computer Science at Queen’s University Belfast, specialising in hardware security, applied cryptography, and side-channel analysis. His research focuses on securing embedded and IoT systems through advanced techniques in machine learning-enhanced side-channel attacks and countermeasures, physical unclonable functions (PUFs), and efficient implementations of both classical and post-quantum cryptography. Dr Hoang supervises doctoral research across these areas and contributes to the development of next-generation secure computing technologies through his publications, collaborations, and engagement with the wider hardware security community.

Dr Craig Allford – is a Research Fellow in Optoelectronics at the School of Physics & Astronomy, Cardiff University. He is currently employed by the EPSRC Future Compound Semiconductor Hub, whose vision is to establish the UK as the primary global research and manufacturing hub for Compound Semiconductor (CS) Technologies. The focus is on the advanced characterisation of laser diodes, and long-term degradation studies of these devices. This work allows us to understand how to improve both the performance, and operating lifetimes of III-V compound semiconductor laser diodes. For this activity we have established an extensive suite of characterisation tools and equipment.

Mr Xiaoyao Song is a Research Associate in Electronics and Communications Engineering at the School of Electrical and Electronic Engineering, University of Sheffield. His work focuses on advanced electronic and communication systems, drawing on his research experience in novel device concepts such as low-power transistors and neuromorphic computing components. He has contributed to research on solid electrolyte transistors and machine learning-assisted modelling of electronic devices, as seen in collaborative publications in materials and electronic systems research.

Dr Prosanta Gope – is an Associate Professor in Cybersecurity in the Department of Computer Science at the University of Sheffield, UK, where he also serves as Course Director for the MSc in Cybersecurity & AI and is a member of the Security of Advanced Systems research group. His research addresses real-world security challenges across lightweight authentication, authenticated encryption, IoT and mobile communications security, privacy-preserving machine learning, smart-grid protection and next-generation network protocols, and he has authored over 100 peer-reviewed publications and holds multiple patents. Prior to Sheffield, Dr Gope was a Research Fellow at the National University of Singapore, and he actively contributes to the cybersecurity community through editorial roles with leading IEEE journals and technical programme leadership at major international conferences.

Dr. Radu Sporea – is an Associate Professor of Power Electronics and Semiconductor Devices at the Advanced Technology Institute (ATI), University of Surrey. Formerly a Royal Academy of Engineering Academic Research Fellow, EPSRC PhD+ Fellow, and PhD researcher at ATI, he previously studied computer systems engineering at “Politehnica” University in Bucharest before working as a design engineer on ultra-low-power CMOS analog circuits for Catalyst Semiconductor (now ON Semiconductor). His research spans advanced large-area semiconductor device design, energy-efficient and neuromorphic hardware, smart sensors and sensor arrays, and paper-based electronics for physical-digital interaction. Alongside his academic work, Radu is an active science communicator, contributing to public engagement through photography, writing, podcasts, YouTube films, and performances at national festivals and events, and has served as a scientific advisor for BBC television. He is a recipient of the British Science Association’s I. K. Brunel Award and has been featured on platforms including Pod Academy, Academic Minute, Pint of Science, Café Scientifique, Bright Club, and BBC4.

Dr Sangeet Saha – is a Lecturer in Embedded Systems in the School of Computer Science and Electronic Engineering at the University of Essex, where he is also a member of the Robotics and Embedded Systems Research Group. His research focuses on real-time and embedded computing, including scheduling strategies for FPGAs and multicore systems, fault tolerance, approximation-based computing and heterogeneous FPGA/GPU systems for efficient deep learning at the edge, and he contributes to multiple ongoing EPSRC-funded projects. Prior to his current role, he held academic positions at the University of Huddersfield and served as a Senior Research Officer at Essex, where he worked on resilient embedded system designs for extreme environments. Dr Saha has published extensively in leading conferences and journals, co-authored a book on real-time scheduling for FPGAs, and has been recognised with awards such as the YERUN Research Mobility Award.

Professor Gareth Howells – is a leading expert in cybersecurity and secure communications, serving as Professor of Cyber Security in the School of Computer Science and Electronic Engineering at the University of Essex, where he has been active in research for over 35 years and published more than 240 technical papers. His core research spans device authentication, biometrics, secure communications and identity management, with his principal contribution being the development of ICMetric techniques that derive digital signatures and encryption keys from physical circuit properties, significantly reducing the need for stored keys and underpinning patented technologies now being commercialised through the spin-out company Metrarc Ltd. His work also encompasses pattern recognition, assistive technologies and AI-related systems for secure and resilient computing, and he supervises advanced research students while securing competitive research funding to advance impactful cybersecurity solutions.

Dr Daniel Fentham – is a Research Assistant in Computer Science at the University of Birmingham, where he recently completed his PhD thesis, “Diversity as a Defence against Neural Network Adversarial Examples.” His current work focuses on video authentication technologies to combat misinformation, building on previous research into the security of facial recognition systems and the use of evolutionary methods to enhance the robustness of image classification networks.

Dr Junqing Zhang – is a Senior Lecturer (Associate Professor) in the School of Computer Science and Informatics at the University of Liverpool, UK, where he leads research on wireless security, physical-layer security, key generation, radio-frequency fingerprint identification, and wireless sensing. He has authored or co-authored over 100 peer-reviewed publications and focuses on developing practical physical-layer security solutions for next-generation wireless systems with ultra-low energy consumption and strong security guarantees, as well as exploring novel sensing applications using Wi-Fi and mmWave radars across a range of IoT technologies. Dr Zhang was co-recipient of the Best Workshop Paper Award at IEEE WCNC 2025, serves as Senior Area Editor for IEEE Transactions on Information Forensics and Security and Associate Editor for IEEE Transactions on Mobile Computing, and has held leadership roles including TPC Symposium Co-Chair for ICNC and ICC conferences and TPC Co-Chair for specialised IEEE workshops.

Dr Cillian McPolin – is a Senior Photonics Technologist at Digital Catapult, the UK’s innovation agency for advanced digital technologies, where he leads efforts to accelerate the adoption and development of integrated and industrial photonics alongside quantum sensing. With more than eight years of experience spanning academia and industry, he has published extensively on nanophotonics, plasmonics and silicon photonics and holds a patent on nanophotonic signal modulation. His work focuses on photonic technologies for high-impact applications such as data storage, sensing and quantum systems, bridging fundamental research with real-world innovation to support the growth of photonics adoption across the UK technology ecosystem.

Dr Sam Shutts – is a Senior Lecturer in the Condensed Matter and Photonics Group within the School of Physics and Astronomy at Cardiff University, where he conducts research in photonics and semiconductor devices focused on lasers and integrated photonic systems. His work includes the design, fabrication and characterisation of III-V quantum dot and VCSEL lasers on silicon and other substrates, contributing to advances in optoelectronics and compound semiconductor technologies, and he has co-authored numerous peer-reviewed publications in leading journals and conferences in these areas. He is also involved in collaborative research projects spanning semiconductor manufacturing and integrated photonics within national research hubs.

Dr Sridhar Adepu – is a Senior Lecturer in Cyber Security in the School of Mathematics and Computer Science at Swansea University, where he conducts research and teaches on the security of cyber-physical systems, industrial control systems and critical infrastructure. His scholarly work addresses real-world challenges in securing complex interconnected systems such as IIoT and industrial networks through multidisciplinary approaches that blend cyber security, formal methods, anomaly detection and resilient system design, and he has published extensively on these topics in leading venues. Prior to Swansea, he was a Lecturer at the University of Bristol and a postdoctoral researcher at the Advanced Digital Sciences Center (affiliated with UIUC), and he has held research fellowships and visiting positions at institutions including the Singapore University of Technology and Design and Carnegie Mellon University. Dr Adepu holds a PhD in Information Systems Technology and Design and remains actively engaged with the wider research and industrial community on critical infrastructure protection and secure systems innovation.

Dr Chongyan Gu is a Senior Lecturer (Associate Professor) in the School of Electronics, Electrical Engineering and Computer Science at Queen’s University Belfast and a member of the Centre for Secure Information Technologies (CSIT), where she leads research in hardware security with a focus on physical unclonable functions (PUFs), true random number generation, hardware Trojan detection, logic obfuscation and machine-learning-assisted attacks and defenses. Her work bridges foundational research and industrial impact, including EPSRC-funded projects and the licensing of PUF technology for secure electronic vehicle charging systems, and her team has won innovation awards for commercialisation potential. Dr Gu’s scholarship has been recognised with an EPSRC New Investigator Award, and she serves on editorial boards and technical programme committees for major IEEE conferences while contributing invited talks, tutorials and high-impact publications in trusted and resilient hardware design.

Prof. Amro Awad is an Associate Professor in Electrical Engineering (with a focus on Digital Technologies) at the University of Oxford and a Tutorial Fellow at University College, where he leads research on secure and high-performance computing architectures. Before joining Oxford in 2024, he was a tenured Associate Professor and head of the Secure and Advanced Computer Architecture (SACA) research group at North Carolina State University, and he has held research and development positions at HP Labs, AMD Research and MediaTek as well as U.S. government laboratories including Los Alamos, Sandia and the Air Force Research Laboratory. His work spans computer architecture, hardware security, hardware/software co-design and system privacy, and he holds multiple U.S. patents, has been inducted into the IEEE TCCA HPCA Hall of Fame, and serves as Associate Editor for ACM Transactions on Architecture and Code Optimization; his research has been featured at major international conferences and recognised with awards including the Bennett Faculty Fellowship and Goodnight Early Career award.

Dr Arnab Kumar Biswas – is a Lecturer in the School of Electronics, Electrical Engineering and Computer Science at Queen’s University Belfast and a member of the Centre for Secure Information Technologies (CSIT), a UK Academic Centre of Excellence in Cyber Security Research. His research spans embedded and network security, hardware–software co-design for secure systems, Internet-of-Things and remote health security, satellite communication security, and quantum-safe and post-quantum cryptographic acceleration, with numerous peer-reviewed contributions to top journals and conferences. At QUB he supervises doctoral research, contributes to EPSRC-funded projects, and develops innovative security solutions that bridge theoretical foundations and practical implementation in hardware and software.

Getting there

Prince Philip House

3 Carlton House Terrace

London

SW1Y 5DG

United Kingdom